## **APPENDICES**

## APPENDICES A

### Microcontroller

Microcontrollers come in many varieties. Depending on the power and features that are needed, one might choose a 4 bit, 8 bit, 16 bit, or 32 bit microcontroller. In addition, some specialized versions are available which include features specific for communications keyboard handling, signal processing, video processing, and other tasks. The examples of different types of commercial microcontroller devices are given in the following tables.

**Table 1.1** 4 Bit Microcontrollers

| Model (Manufacturer)         | I/O | Pins | RAM (bytes) | ROM (bytes) | Counters | Extra Features |

|------------------------------|-----|------|-------------|-------------|----------|----------------|

| COP400 Family (National)     | 23  | 28   | 64          | 1K          | 1        | Serial bit I/O |

| HMCS40 (Hitachi)             | 10  | 28   | 32          | 512         | -        | 10-bit ROM     |

| TMS 1000 (Texas Instruments) | 23  | 28   | 64          | 1K          | -        | LED display    |

**Table 1.2** 8 Bit Microcontrollers

| Model (Manufacturer)     | I/O | Pins | RAM (bytes) | ROM (bytes) | Counters | Extra Features                                                    |

|--------------------------|-----|------|-------------|-------------|----------|-------------------------------------------------------------------|

| 8048 (Intel)             | 27  | 40   | 64          | 1K          | 1        | 8k External memory                                                |

| 8051 (Intel)             | 32  | 40   | 128         | 4K          | 2        | 128k External memory, Boolean processing, serial port             |

| COP800 Family (National) | 24  | 28   | 64          | 1K          | 1        | Serial bit I/O, 8-channel A/D converter                           |

| 6805 (Motorola)          | 20  | 28   | 64          | 1K          | 1        | PLL frequency synthesizer,                                        |

| 68hc11(Motorola)         | 40  | 52   | 256         | 8K          | 2        | A/D, PWM generator, pulse accumulator                             |

| TMS370 (Texas)           | 55  | 68   | 256         | 4K          | 2        | watchdog timer, Instruments) Serial ports, A/D (8 bit, 8 channel) |

| PIC (Micro Chip)         | 12  | 18   | 25          | 1K          | 0        | small pin count, very low power consumption                       |

---

**Table 1.3. 16 Bit Microcontrollers**

| Model<br>(Manufacturer)  | I/O | Pins | RAM (bytes) | ROM (bytes) | Counters | Extra Features                                            |

|--------------------------|-----|------|-------------|-------------|----------|-----------------------------------------------------------|

| 80c196 (Intel)           | 40  | 68   | 232 8K      | 2           |          | PWM generator, watchdog timer                             |

| HPC Family<br>(National) | 52  | 68   | 512 16K     | 4           |          | PWM generator, watchdog timer, 8-channel A/D, serial port |

### **AT mega 16 Feature:**

1-High-performance, Low-power AVR® 8-bit Microcontroller.

2-Advanced RISC Architecture.

- 131 Powerful Instructions.

- Most Single Most Single.

- clock Cycle Execution.

- 32x 8 General Purpose Working Registers.

- Fully Static Operation.

- Up to 16 MIPS Throughput at 16 MHz.

- On-chip 2-cycle Multiplier.

3-High Endurance Non-volatile Memory segments:

- 16K Bytes of In-System Self-programmable Flash program memory.

- 512 Bytes EEPROM.

- 1K Byte Internal SRAM.

- Write/Erase Cycles: 10,000 Flash/100,000 EEPROM.

- Data retention: 20 years at 85°C/100years at 25°C.

- Optional Boot Code Section with Independent Lock Bits.

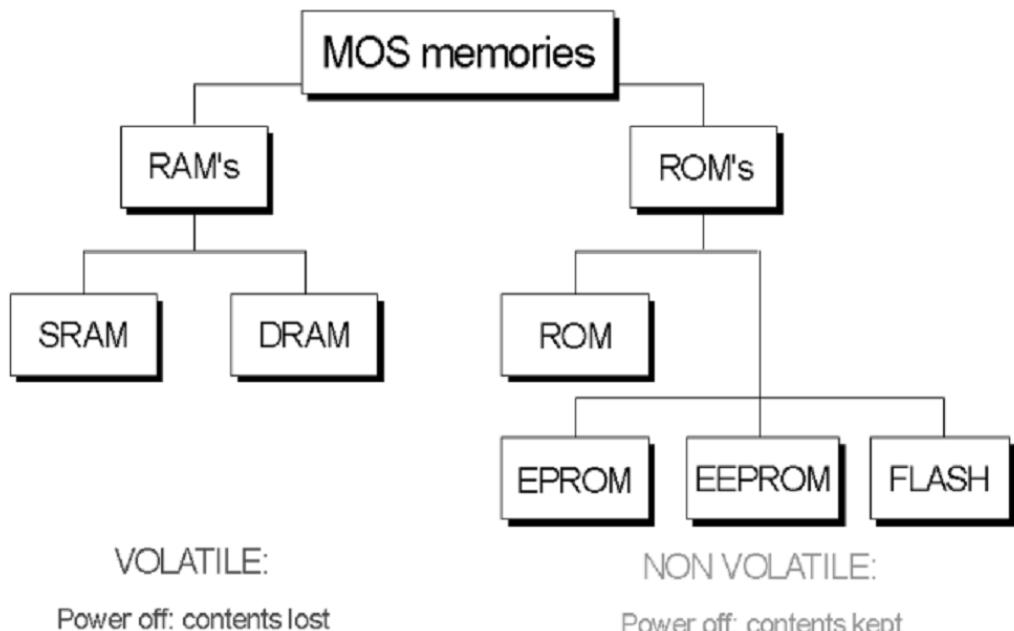

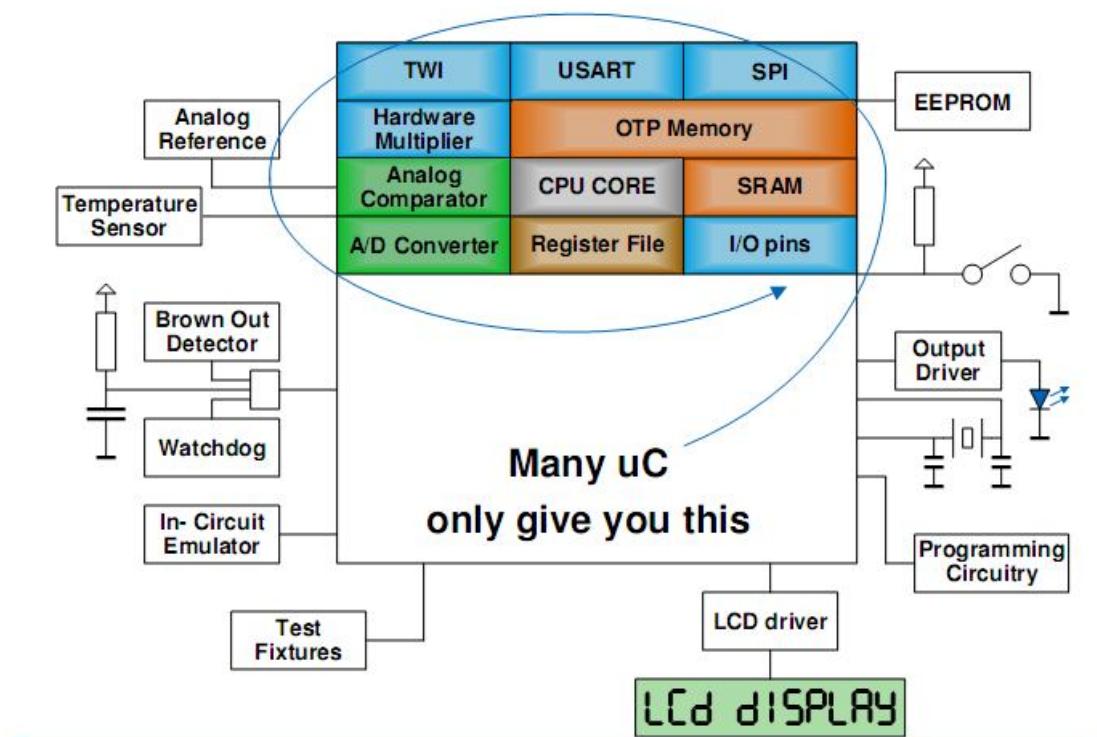

Figure :complementary metal-oxide-simeconductor(CMOS).

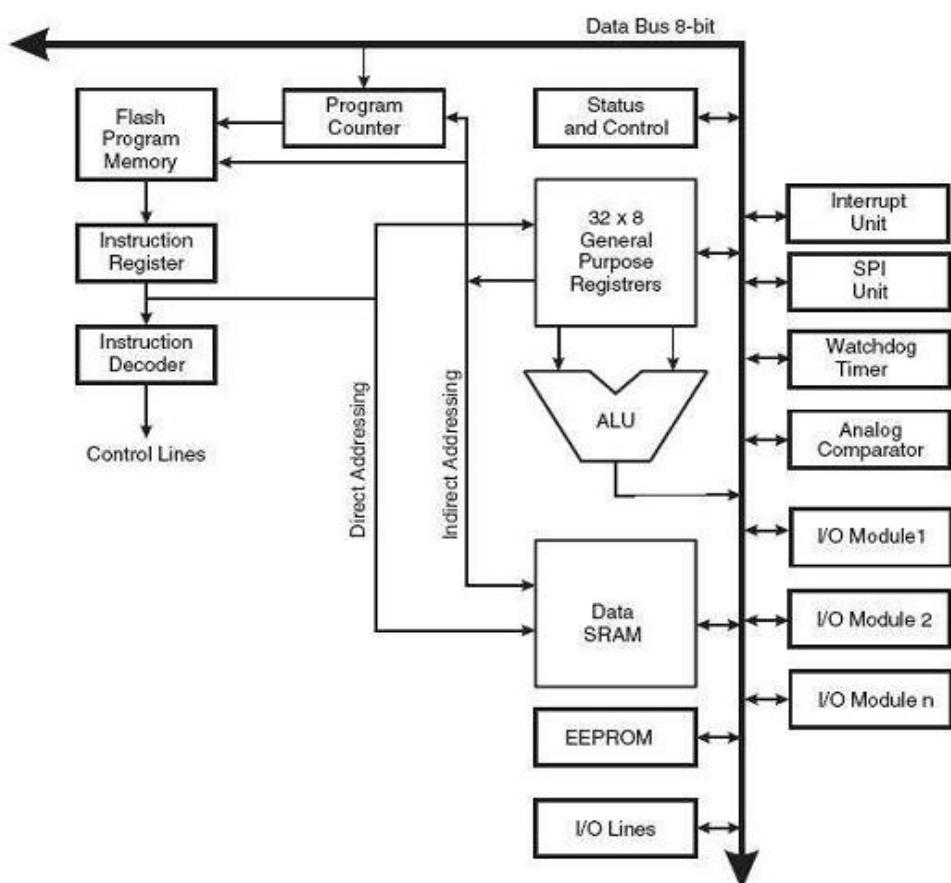

Figure: ATmega16 Architecture.

## AVR Microcontroller

## Register Summary

| Address     | Name | Bit 7                                       | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Page |

|-------------|------|---------------------------------------------|-------|-------|-------|-------|-------|-------|-------|------|

| \$01 (\$21) | TWSR | TWS7                                        | TWS6  | TWS5  | TWS4  | TWS3  | -     | TWPS1 | TWPS0 | 179  |

| \$00 (\$20) | TWBR | Two-wire Serial Interface Bit Rate Register |       |       |       |       |       |       |       | 178  |

Notes:

1. When the OCDEN Fuse is unprogrammed, the OSCCAL Register is always accessed on this address. Refer to the debugger specific documentation for details on how to use the OCDR Register.

2. Refer to the USART description for details on how to access UBRRH and UCSRC.

3. For compatibility with future devices, reserved bits should be written to zero if accessed. Reserved I/O memory addresses should never be written.

4. Some of the Status Flags are cleared by writing a logical one to them. Note that the CBI and SBI instructions will operate on all bits in the I/O Register, writing a one back into any flag read as set, thus clearing the flag. The CBI and SBI instructions work with registers \$00 to \$1F only.

## Instruction Set Summary

| Mnemonics                         | Operands | Description                              | Operation                                                  | Flags     | #Clocks |

|-----------------------------------|----------|------------------------------------------|------------------------------------------------------------|-----------|---------|

| ARITHMETIC AND LOGIC INSTRUCTIONS |          |                                          |                                                            |           |         |

| ADD                               | Rd, Rr   | Add two Registers                        | $Rd \leftarrow Rd + Rr$                                    | Z,C,N,V,H | 1       |

| ADC                               | Rd, Rr   | Add with Carry two Registers             | $Rd \leftarrow Rd + Rr + C$                                | Z,C,N,V,H | 1       |

| ADIW                              | Rd,K     | Add Immediate to Word                    | $Rd(Rd \leftarrow Rd + Rr + K)$                            | Z,C,N,V,S | 2       |

| SUB                               | Rd, Rr   | Subtract two Registers                   | $Rd \leftarrow Rd - Rr$                                    | Z,C,N,V,H | 1       |

| SUBI                              | Rd, K    | Subtract Constant from Register          | $Rd \leftarrow Rd - K$                                     | Z,C,N,V,H | 1       |

| SBC                               | Rd, Rr   | Subtract with Carry two Registers        | $Rd \leftarrow Rd - Rr - C$                                | Z,C,N,V,H | 1       |

| SBCI                              | Rd, K    | Subtract with Carry Constant from Reg.   | $Rd \leftarrow Rd - K - C$                                 | Z,C,N,V,H | 1       |

| SBIW                              | Rd,K     | Subtract Immediate from Word             | $Rd(Rd \leftarrow Rd - Rr - K)$                            | Z,C,N,V,S | 2       |

| AND                               | Rd, Rr   | Logical AND Registers                    | $Rd \leftarrow Rd \wedge Rr$                               | Z,N,V     | 1       |

| ANDI                              | Rd, K    | Logical AND Register and Constant        | $Rd \leftarrow Rd \wedge K$                                | Z,N,V     | 1       |

| OR                                | Rd, Rr   | Logical OR Registers                     | $Rd \leftarrow Rd \vee Rr$                                 | Z,N,V     | 1       |

| ORI                               | Rd, K    | Logical OR Register and Constant         | $Rd \leftarrow Rd \vee K$                                  | Z,N,V     | 1       |

| EOR                               | Rd, Rr   | Exclusive OR Registers                   | $Rd \leftarrow Rd \oplus Rr$                               | Z,N,V     | 1       |

| COM                               | Rd       | One's Complement                         | $Rd \leftarrow \text{SF} - Rd$                             | Z,C,N,V   | 1       |

| NEG                               | Rd       | Two's Complement                         | $Rd \leftarrow \text{SF} - Rd$                             | Z,C,N,V,H | 1       |

| BSR                               | Rd,K     | Set Bit(s) in Register                   | $Rd \leftarrow Rd \vee K$                                  | Z,N,V     | 1       |

| BSR                               | Rd,K     | Clear Bit(s) in Register                 | $Rd \leftarrow Rd \wedge (\text{SF} - K)$                  | Z,N,V     | 1       |

| INC                               | Rd       | Increment                                | $Rd \leftarrow Rd + 1$                                     | Z,N,V     | 1       |

| DEC                               | Rd       | Decrement                                | $Rd \leftarrow Rd - 1$                                     | Z,N,V     | 1       |

| TST                               | Rd       | Test for Zero or Minus                   | $Rd \leftarrow Rd + Rd$                                    | Z,N,V     | 1       |

| CIR                               | Rd       | Clear Register                           | $Rd \leftarrow Rd \wedge Rd$                               | Z,N,V     | 1       |

| SET                               | Rd       | Set Register                             | $Rd \leftarrow \text{SF}$                                  | None      | 1       |

| MUL                               | Rd, Rr   | Multiply Unsigned                        | $R1:R0 \leftarrow Rd \times Rr$                            | Z,C       | 2       |

| MULS                              | Rd, Rr   | Multiply Signed                          | $R1:R0 \leftarrow Rd \times Rr$                            | Z,C       | 2       |

| MULSU                             | Rd, Rr   | Multiply Signed with Unsigned            | $R1:R0 \leftarrow Rd \times Rr$                            | Z,C       | 2       |

| FMUL                              | Rd, Rr   | Fractional Multiply Unsigned             | $R1:R0 \leftarrow (Rd \times Rr) \ll 1$                    | Z,C       | 2       |

| FMULS                             | Rd, Rr   | Fractional Multiply Signed               | $R1:R0 \leftarrow (Rd \times Rr) \ll 1$                    | Z,C       | 2       |

| FMULSU                            | Rd, Rr   | Fractional Multiply Signed with Unsigned | $R1:R0 \leftarrow (Rd \times Rr) \ll 1$                    | Z,C       | 2       |

| BRANCH INSTRUCTIONS               |          |                                          |                                                            |           |         |

| BRJP                              | X        | Relative Jump                            | $PC \leftarrow PC + k + 1$                                 | None      | 2       |

| BRJP                              |          | Indirect Jump to (Z)                     | $PC \leftarrow Z$                                          | None      | 2       |

| JMP                               | X        | Direct Jump                              | $PC \leftarrow k$                                          | None      | 3       |

| RCALL                             | X        | Relative Subroutine Call                 | $PC \leftarrow PC + k + 1$                                 | None      | 3       |

| ICALL                             |          | Indirect Call to (Z)                     | $PC \leftarrow Z$                                          | None      | 3       |

| CALL                              | X        | Direct Subroutine Call                   | $PC \leftarrow k$                                          | None      | 4       |

| RET                               |          | Subroutine Return                        | $PC \leftarrow \text{STACK}$                               | None      | 4       |

| RETI                              |          | Interrupt Return                         | $PC \leftarrow \text{STACK}$                               | I         | 4       |

| CPSE                              | Rd,Rr    | Compare, Skip if Equal                   | $I(Rd = Rr) PC \leftarrow PC + k + 3$                      | None      | 1/2/3   |

| CP                                | Rd,Rr    | Compare                                  | $Rd = Rr$                                                  | Z,N,V,C,H | 1       |

| CPO                               | Rd,Rr    | Compare with Carry                       | $Rd = Rr - C$                                              | Z,N,V,C,H | 1       |

| CPI                               | Rd,K     | Compare Register with Immediate          | $Rd = K$                                                   | Z,N,V,C,H | 1       |

| BRSC                              | Rr,b     | Skip if Bit in Register Cleared          | $I(Rn(b) = 0) PC \leftarrow PC + k + 3$                    | None      | 1/2/3   |

| BRBS                              | Rr,b     | Skip if Bit in Register is Set           | $I(Rn(b) = 1) PC \leftarrow PC + k + 3$                    | None      | 1/2/3   |

| BRSC                              | Rr,b     | Skip if Bit in IO Register Cleared       | $I(Rn(b) = 0) PC \leftarrow PC + k + 3$                    | None      | 1/2/3   |

| BRBS                              | Rr,b     | Skip if Bit in IO Register is Set        | $I(Rn(b) = 1) PC \leftarrow PC + k + 3$                    | None      | 1/2/3   |

| BRSS                              | a, k     | Branch i Status Flag Set                 | $I(SREQ(a) = 1) \text{ then } PC \leftarrow PC + k + 1$    | None      | 1/2     |

| BRSC                              | a, k     | Branch i Status Flag Cleared             | $I(SREQ(a) = 0) \text{ then } PC \leftarrow PC + k + 1$    | None      | 1/2     |

| BRZ                               | k        | Branch if Equal                          | $I(Z = 1) \text{ then } PC \leftarrow PC + k + 1$          | None      | 1/2     |

| BRNE                              | k        | Branch if Not Equal                      | $I(Z = 0) \text{ then } PC \leftarrow PC + k + 1$          | None      | 1/2     |

| BRCS                              | k        | Branch if Carry Set                      | $I(C = 1) \text{ then } PC \leftarrow PC + k + 1$          | None      | 1/2     |

| BRCC                              | k        | Branch if Carry Cleared                  | $I(C = 0) \text{ then } PC \leftarrow PC + k + 1$          | None      | 1/2     |

| BRSH                              | k        | Branch if Same or Higher                 | $I(C = 0) \text{ then } PC \leftarrow PC + k + 1$          | None      | 1/2     |

| BRLO                              | k        | Branch if Lower                          | $I(C = 1) \text{ then } PC \leftarrow PC + k + 1$          | None      | 1/2     |

| BRVI                              | k        | Branch if Minus                          | $I(N = 1) \text{ then } PC \leftarrow PC + k + 1$          | None      | 1/2     |

| BRPL                              | k        | Branch if Plus                           | $I(N = 0) \text{ then } PC \leftarrow PC + k + 1$          | None      | 1/2     |

| BRGE                              | k        | Branch i Greater or Equal Signed         | $I(N \oplus V = 0) \text{ then } PC \leftarrow PC + k + 1$ | None      | 1/2     |

| BRLT                              | k        | Branch if Less Than Zero, Signed         | $I(N \oplus V = 1) \text{ then } PC \leftarrow PC + k + 1$ | None      | 1/2     |

| BRHS                              | k        | Branch if Half Carry Flag Set            | $I(H = 1) \text{ then } PC \leftarrow PC + k + 1$          | None      | 1/2     |

| BRHC                              | k        | Branch if Half Carry Flag Cleared        | $I(H = 0) \text{ then } PC \leftarrow PC + k + 1$          | None      | 1/2     |

| BRIS                              | k        | Branch i If Flag Set                     | $I(T = 1) \text{ then } PC \leftarrow PC + k + 1$          | None      | 1/2     |

| BRIC                              | k        | Branch i If Flag Cleared                 | $I(T = 0) \text{ then } PC \leftarrow PC + k + 1$          | None      | 1/2     |

| BRIS                              | k        | Branch i Overflow Flag is Set            | $I(V = 1) \text{ then } PC \leftarrow PC + k + 1$          | None      | 1/2     |

| BRVC                              | k        | Branch i Overflow Flag is Cleared        | $I(V = 0) \text{ then } PC \leftarrow PC + k + 1$          | None      | 1/2     |

| Mnemonics                            | Operands | Description                      | Operation                                                          | Flags      | #Clocks |

|--------------------------------------|----------|----------------------------------|--------------------------------------------------------------------|------------|---------|

| SBE                                  | x        | Branch If Emulator Enabled       | $PC \leftarrow PC + x + 1$                                         | None       | 1 / 2   |

| BRD                                  | x        | Branch If Emulator Disabled      | $PC \leftarrow PC + x + 1$                                         | None       | 1 / 2   |

| <b>DATA TRANSFER INSTRUCTIONS</b>    |          |                                  |                                                                    |            |         |

| MOV                                  | Rd, Rr   | Move Between Registers           | $Rd \leftarrow Rr$                                                 | None       | 1       |

| MOVW                                 | Rd, Rr   | Copy Register Word               | $Rd \leftarrow Rr \leftarrow Rr + 1:Rr$                            | None       | 1       |

| LDI                                  | Rd, K    | Load Immediate                   | $Rd \leftarrow K$                                                  | None       | 1       |

| LD                                   | Rd, X    | Load Indirect                    | $Rd \leftarrow (X)$                                                | None       | 2       |

| LD                                   | Rd, X+   | Load Indirect and Post-Inc       | $Rd \leftarrow (X), X \leftarrow X + 1$                            | None       | 2       |

| LD                                   | Rd, -X   | Load Indirect and Pre-Dec        | $X \leftarrow X - 1, Rd \leftarrow (X)$                            | None       | 2       |

| LD                                   | Rd, Y    | Load Indirect                    | $Rd \leftarrow (Y)$                                                | None       | 2       |

| LD                                   | Rd, Y+   | Load Indirect and Post-Inc       | $Rd \leftarrow (Y), Y \leftarrow Y + 1$                            | None       | 2       |

| LD                                   | Rd, -Y   | Load Indirect and Pre-Dec        | $Y \leftarrow Y - 1, Rd \leftarrow (Y)$                            | None       | 2       |

| LDQ                                  | Rd, Y#q  | Load Indirect with Displacement  | $Rd \leftarrow (Y + q)$                                            | None       | 2       |

| LD                                   | Rd, Z    | Load Indirect                    | $Rd \leftarrow (Z)$                                                | None       | 2       |

| LD                                   | Rd, Z+   | Load Indirect and Post-Inc       | $Rd \leftarrow (Z), Z \leftarrow Z + 1$                            | None       | 2       |

| LD                                   | Rd, -Z   | Load Indirect and Pre-Dec        | $Z \leftarrow Z - 1, Rd \leftarrow (Z)$                            | None       | 2       |

| LDQ                                  | Rd, Z#q  | Load Indirect with Displacement  | $Rd \leftarrow (Z + q)$                                            | None       | 2       |

| LDS                                  | Rd, x    | Load Direct from SRAM            | $Rd \leftarrow (x)$                                                | None       | 2       |

| ST                                   | X, Rr    | Store Indirect                   | $(X) \leftarrow Rr$                                                | None       | 2       |

| ST                                   | Xt, Rr   | Store Indirect and Post-Inc      | $(X) \leftarrow Rr, X \leftarrow X + 1$                            | None       | 2       |

| ST                                   | -X, Rr   | Store Indirect and Pre-Dec       | $X \leftarrow X - 1, (X) \leftarrow Rr$                            | None       | 2       |

| ST                                   | Y, Rr    | Store Indirect                   | $(Y) \leftarrow Rr$                                                | None       | 2       |

| ST                                   | -Y, Rr   | Store Indirect and Post-Inc      | $(Y) \leftarrow Rr, Y \leftarrow Y + 1$                            | None       | 2       |

| STD                                  | Y#q, Rr  | Store Indirect with Displacement | $(Y + q) \leftarrow Rr$                                            | None       | 2       |

| ST                                   | Z, Rr    | Store Indirect                   | $(Z) \leftarrow Rr$                                                | None       | 2       |

| ST                                   | Z+, Rr   | Store Indirect and Post-Inc      | $(Z) \leftarrow Rr, Z \leftarrow Z + 1$                            | None       | 2       |

| ST                                   | -Z, Rr   | Store Indirect and Pre-Dec       | $Z \leftarrow Z - 1, (Z) \leftarrow Rr$                            | None       | 2       |

| STD                                  | Z#q, Rr  | Store Indirect with Displacement | $(Z + q) \leftarrow Rr$                                            | None       | 2       |

| STS                                  | x, Rr    | Store Direct to SRAM             | $(x) \leftarrow Rr$                                                | None       | 2       |

| UPW                                  |          | Load Program Memory              | $R0 \leftarrow (Z)$                                                | None       | 3       |

| UPW                                  | Rd, Z    | Load Program Memory              | $Rd \leftarrow (Z)$                                                | None       | 3       |

| UPW                                  | Rd, Z+   | Load Program Memory and Post-Inc | $Rd \leftarrow (Z), Z \leftarrow Z + 1$                            | None       | 3       |

| SPW                                  |          | Store Program Memory             | $(Z) \leftarrow R1:R0$                                             | None       | -       |

| IN                                   | Rd, P    | In Port                          | $Rd \leftarrow P$                                                  | None       | 1       |

| OUT                                  | P, Rr    | Out Port                         | $P \leftarrow Rr$                                                  | None       | 1       |

| PUSH                                 | Rr       | Push Register on Stack           | STACK $\leftarrow Rr$                                              | None       | 2       |

| POP                                  | Rd       | Po Register from Stack           | $Rd \leftarrow \text{STACK}$                                       | None       | 2       |

| <b>BIT AND BIT-TEST INSTRUCTIONS</b> |          |                                  |                                                                    |            |         |

| BSI                                  | P, b     | Set Bit in I/O Register          | $IO(P, b) \leftarrow 1$                                            | None       | 2       |

| BSI                                  | P, b     | Clear Bit in I/O Register        | $IO(P, b) \leftarrow 0$                                            | None       | 2       |

| LSL                                  | Rd       | Logical Shift Left               | $Rd(n) \leftarrow Rd(n), Rd(0) \leftarrow 0$                       | Z, C, N, V | 1       |

| LSR                                  | Rd       | Logical Shift Right              | $Rd(n) \leftarrow Rd(n), Rd(7) \leftarrow 0$                       | Z, C, N, V | 1       |

| ROL                                  | Rd       | Rotate Left Through Carry        | $Rd(0) \leftarrow C, Rd(n+1) \leftarrow Rd(n), C \leftarrow Rd(7)$ | Z, C, N, V | 1       |

| ROD                                  | Rd       | Rotate Right Through Carry       | $Rd(7) \leftarrow C, Rd(n) \leftarrow Rd(n+1), C \leftarrow Rd(0)$ | Z, C, N, V | 1       |

| ASR                                  | Rd       | Arithmetic Shift Right           | $Rd(n) \leftarrow Rd(n), n \neq 8$                                 | Z, C, N, V | 1       |

| SWAP                                 | Rd       | Swap Nibbles                     | $Rd(3, 0) \leftarrow Rd(7, 4), Rd(7, 4) \leftarrow Rd(3, 0)$       | None       | 1       |

| BSBT                                 | x        | Flag Set                         | $SREG(x) \leftarrow 1$                                             | SREG(x)    | 1       |

| BCUR                                 | x        | Flag Clear                       | $SREG(x) \leftarrow 0$                                             | SREG(x)    | 1       |

| BSI                                  | Rd, b    | Bit Store from Register to T     | $T \leftarrow Rd(b)$                                               | T          | 1       |

| BLO                                  | Rd, b    | Bit Load from T to Register      | $Rd(b) \leftarrow T$                                               | None       | 1       |

| BCO                                  |          | Set Carry                        | $C \leftarrow 1$                                                   | C          | 1       |

| BCO                                  |          | Clear Carry                      | $C \leftarrow 0$                                                   | C          | 1       |

| BNF                                  |          | Set Negative Flag                | $N \leftarrow 1$                                                   | N          | 1       |

| CNF                                  |          | Clear Negative Flag              | $N \leftarrow 0$                                                   | N          | 1       |

| BZ                                   |          | Set Zero Flag                    | $Z \leftarrow 1$                                                   | Z          | 1       |

| CZ                                   |          | Clear Zero Flag                  | $Z \leftarrow 0$                                                   | Z          | 1       |

| BSI                                  |          | Global Interrupt Enable          | $I \leftarrow 1$                                                   | I          | 1       |

| CGI                                  |          | Global Interrupt Disable         | $I \leftarrow 0$                                                   | I          | 1       |

| BTS                                  |          | Set Signed Test Flag             | $S \leftarrow 1$                                                   | S          | 1       |

| CLS                                  |          | Clear Signed Test Flag           | $S \leftarrow 0$                                                   | S          | 1       |

| BEV                                  |          | Set Twice Complement Overflow    | $V \leftarrow 1$                                                   | V          | 1       |

| CLV                                  |          | Clear Twice Complement Overflow  | $V \leftarrow 0$                                                   | V          | 1       |

| SET                                  |          | Set T in SREG                    | $T \leftarrow 1$                                                   | T          | 1       |

| CLT                                  |          | Clear T in SREG                  | $T \leftarrow 0$                                                   | T          | 1       |

| SEH                                  |          | Set Half Carry Flag in SREG      | $H \leftarrow 1$                                                   | H          | 1       |

| Mnemonics                       | Operands | Description                   | Operation                                | Flags | #Clocks |

|---------------------------------|----------|-------------------------------|------------------------------------------|-------|---------|

| CLH                             |          | Clear Half Carry Flag in SREG | $H \leftarrow 0$                         | H     | 1       |

| <b>MCU CONTROL INSTRUCTIONS</b> |          |                               |                                          |       |         |

| NOP                             |          | No Operation                  |                                          | None  | 1       |

| SLEEP                           |          | Sleep                         | (see specific descr. for Sleep function) | None  | 1       |

| WDR                             |          | Watchdog Reset                | (see specific descr. for WDR(timer))     | None  | 1       |

| BREAK                           |          | Break                         | For On-Chip Debug Only                   | None  | N/A     |

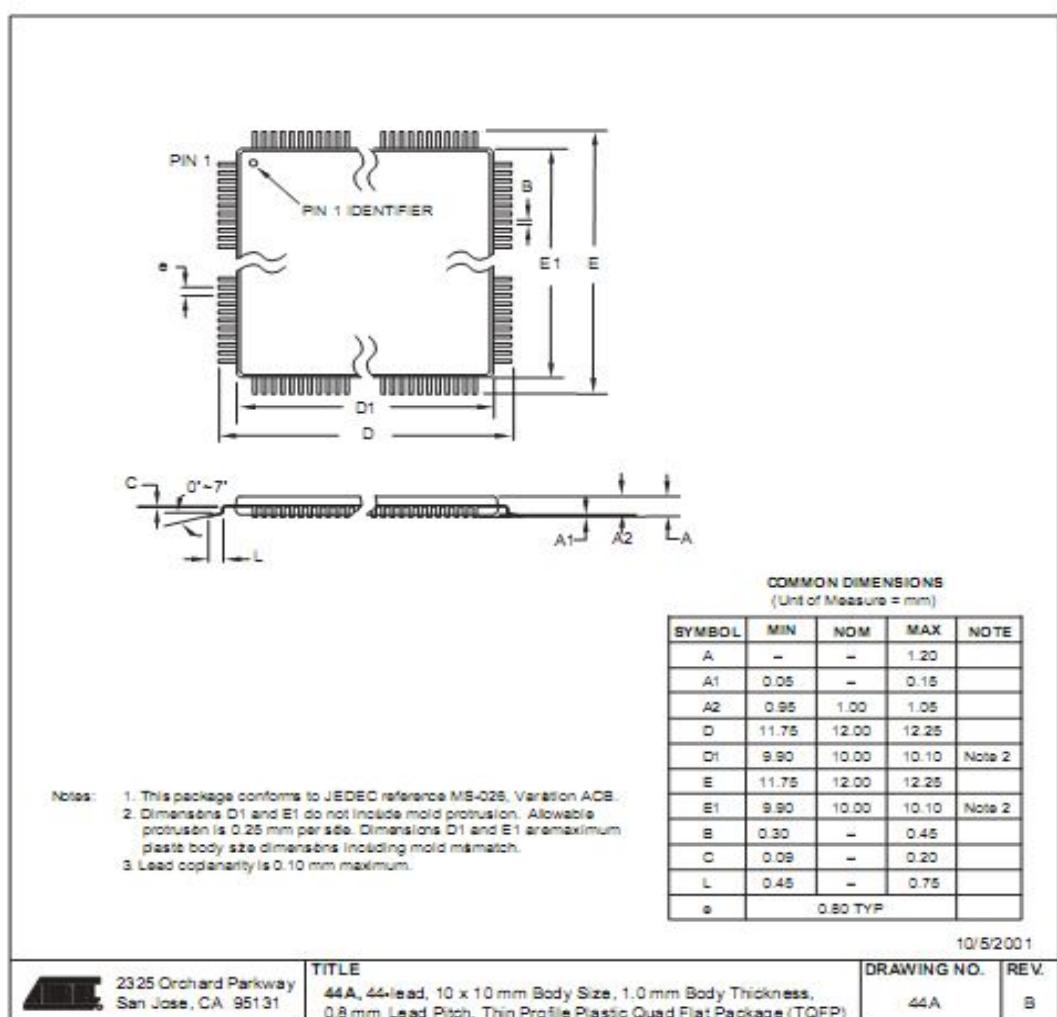

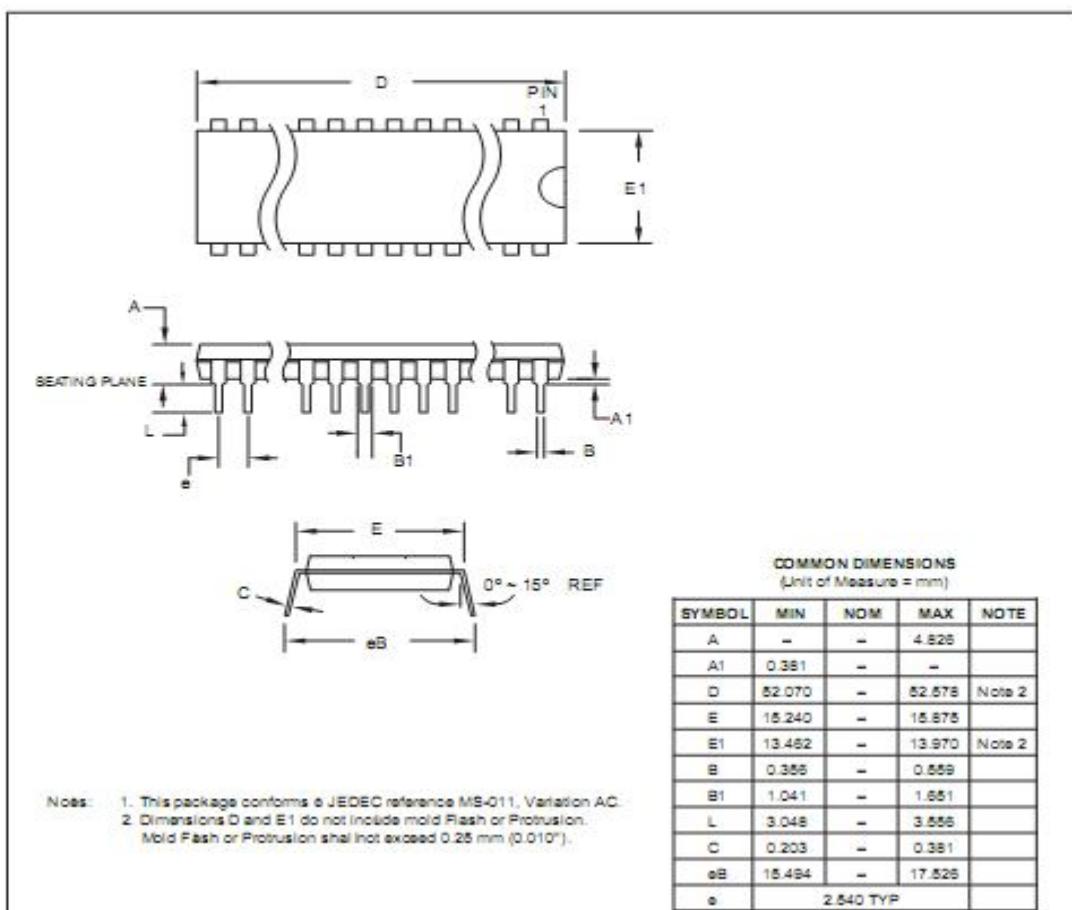

## Packaging Information

44A

## Ordering Information

| Speed (MHz) | Power Supply | Ordering Code | Package | Operation Range               |

|-------------|--------------|---------------|---------|-------------------------------|

| 8           | 2.7 - 5.5V   | ATmega16L-8AC | 44A     | Commercial<br>(0°C to 70°C)   |

|             |              | ATmega16L-8PC | 40P6    | Industrial<br>(-40°C to 85°C) |

|             |              | ATmega16L-8MC | 44M1    |                               |

|             | 4.5 - 5.5V   | ATmega16L-8AI | 44A     | Industrial<br>(-40°C to 85°C) |

|             |              | ATmega16L-8PI | 40P6    |                               |

|             |              | ATmega16L-8MI | 44M1    |                               |

| 16          | 4.5 - 5.5V   | ATmega16-16AC | 44A     | Commercial<br>(0°C to 70°C)   |

|             |              | ATmega16-16PC | 40P6    | Industrial<br>(-40°C to 85°C) |

|             | 4.5 - 5.5V   | ATmega16-16MC | 44M1    |                               |

|             |              | ATmega16-16AI | 44A     | Industrial<br>(-40°C to 85°C) |

|             |              | ATmega16-16PI | 40P6    |                               |

|             |              | ATmega16-16MI | 44M1    |                               |

## Code Size and Execution Time

| Device    | Max Speed<br>[MHz] | Code Size<br>[Bytes] | Cycles | Execution Time<br>[ $\mu$ s] |

|-----------|--------------------|----------------------|--------|------------------------------|

| ATmega16  | 16                 | 32                   | 227    | 14.2                         |

| MSP430    | 8                  | 34                   | 246    | 30.8                         |

| T89C51RD2 | 20                 | 57                   | 4200   | 210.0                        |

| PIC18F452 | 40                 | 92                   | 716    | 17.9                         |

| PIC16C74  | 20                 | 87                   | 2492   | 124.6                        |

| 68HC11    | 12                 | 59                   | 1238   | 103.2                        |

## APPENDICES B

### Relays

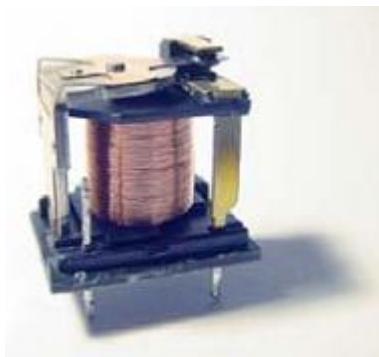

A relay is an electrical switch that uses an electromagnet to move the switch from the off to one position instead of a person moving the switch. It takes a relatively small amount of power to turn on a relay but the relay can control something that draws much more power. Ex: A relay is used to control the air conditioner in your home. The AC unit probably runs off of 220VAC at around 30A. That's 6600 Watts! The coil that controls the relay may only need a few watts to pull the contacts together.

Figure: relay

This is the schematic representation of a relay. The contacts at the top are normally open (i.e. not connected). When current is passed through the coil it creates a magnetic field that pulls the switch closed (i.e. connects the top contacts). Usually a spring will pull the switch open again once the power is removed from the coil.

## OPERATING PRINCIPLES

There are really only two fundamentally different operating principles:

(1) electro-magnetic attraction:

Operate by virtue of a plunger being drawn into a solenoid, or an armature being attracted to the poles of an electromagnet. Such relays may be actuated by d-c or by a-c quantities.

(2) Electromagnetic-induction relays:

Use the principle of the induction motor whereby torque

is developed by induction in a rotor; this operating principle applies only to relays actuated by alternating current, and in dealing with those relays we shall call them simply "induction-type" relays.

### **Relay Selection**

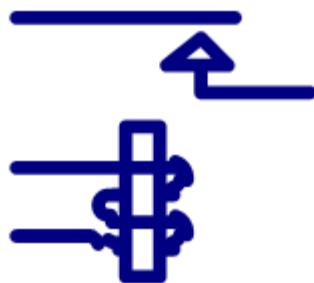

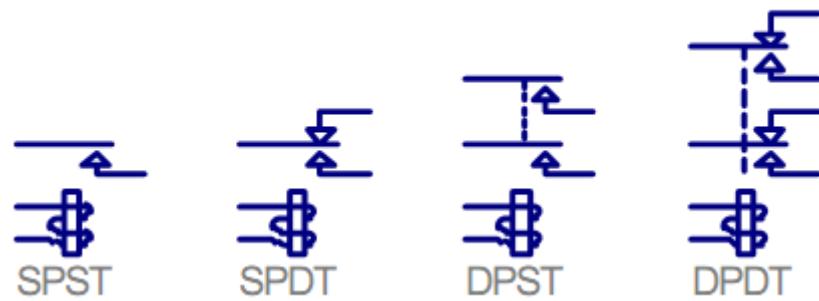

Relays (and switches) come in different configurations. The most common are shown in figure .Single Pole Single Throw (SPST) is the simplest with only two contacts. Single Pole Double Throw (SPDT) has three contacts. The contacts are usually labeled Common (COM), Normally Open (NO), and Normally Closed (NC).

The Normally Closed contact will be connected to the Common

Contact when no power is applied to the coil. The Normally Open contact will be open (i.e. not connected) when no power is applied to the coil. When the coil is energized the Common is connected to the Normally Open contact and the Normally Closed contact is left floating. The Double Pole versions are the same as the Single Pole version except there are two switches that open and close together.[16]

Select a relay with contacts that can handle the voltage and current requirements of the load. Keep in mind that some loads (such as motors) draw much more current when first turned on than they do at

Steady state. Select a relay with a coil voltage and current that you can control easily. Ex: If you want to turn on the AC unit with a 12VDC power supply get a 12VDC coil. Note: Coils will be rated for either AC or DC operation.

Figure: relays type.

Figure: relays parts.

## APPINDICES C

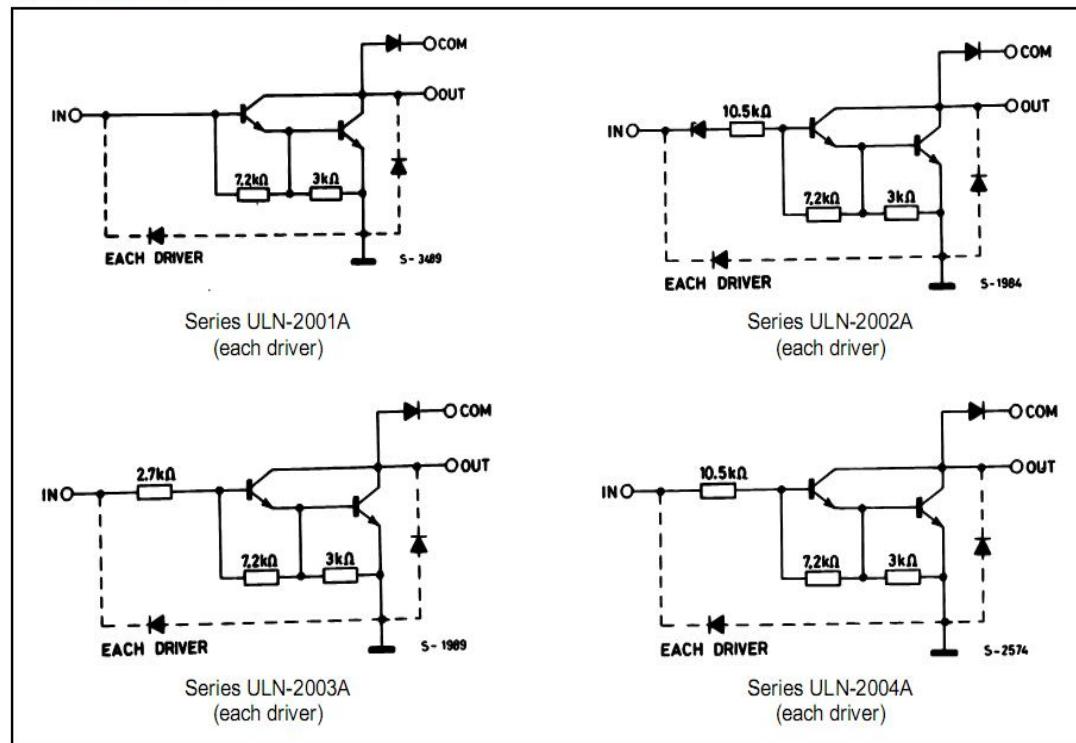

### ULN2003 A

#### SCHEMATIC DIAGRAM

#### ABSOLUTE MAXIMUM RATINGS

| Symbol    | Parameter                                          | Value       | Unit |

|-----------|----------------------------------------------------|-------------|------|

| $V_o$     | Output Voltage                                     | 50          | V    |

| $V_{in}$  | Input Voltage (for ULN2002A/D - 2003A/D - 2004A/D) | 30          | V    |

| $I_c$     | Continuous Collector Current                       | 500         | mA   |

| $I_b$     | Continuous Base Current                            | 25          | mA   |

| $T_{amb}$ | Operating Ambient Temperature Range                | - 20 to 85  | °C   |

| $T_{stg}$ | Storage Temperature Range                          | - 55 to 150 | °C   |

| $T_j$     | Junction Temperature                               | 150         | °C   |

#### THERMAL DATA

| Symbol         | Parameter                           | DIP16 | SO16 | Unit |

|----------------|-------------------------------------|-------|------|------|

| $R_{th,j-amb}$ | Thermal Resistance Junction-ambient | Max.  | 70   | °C/W |

**ELECTRICAL CHARACTERISTICS ( $T_{amb} = 25^\circ\text{C}$  unless otherwise specified)**

| Symbol               | Parameter                            | Test Conditions                                                                                                                                                      | Min. | Typ.              | Max.              | Unit          | Fig.        |

|----------------------|--------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------------------|-------------------|---------------|-------------|

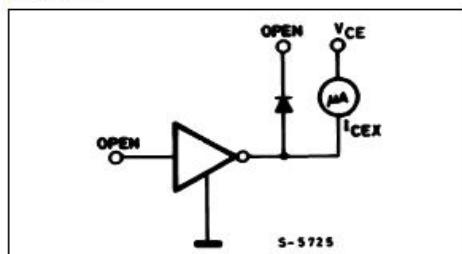

| $I_{CEX}$            | Output Leakage Current               | $V_{CE} = 50\text{V}$<br>$T_{amb} = 70^\circ\text{C}$ , $V_{CE} = 50\text{V}$                                                                                        |      |                   | 50<br>100         | $\mu\text{A}$ | 1a<br>1a    |

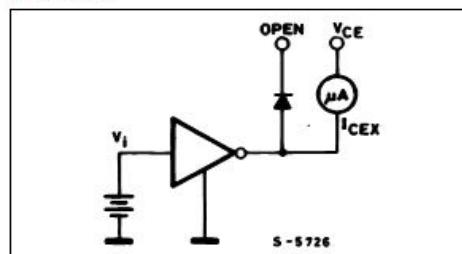

|                      |                                      | $T_{amb} = 70^\circ\text{C}$<br>for <b>ULN2002A</b><br>$V_{CE} = 50\text{V}$ , $V_i = 6\text{V}$<br>for <b>ULN2004A</b><br>$V_{CE} = 50\text{V}$ , $V_i = 1\text{V}$ |      |                   | 500               | $\mu\text{A}$ | 1b          |

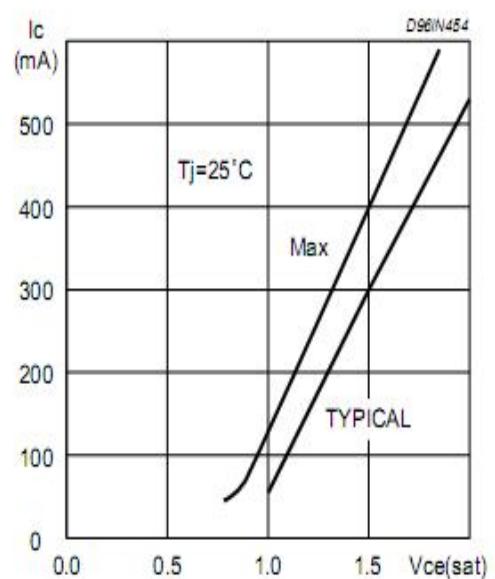

| $V_{CE(\text{sat})}$ | Collector-emitter Saturation Voltage | $I_C = 100\text{mA}$ , $I_B = 250\mu\text{A}$<br>$I_C = 200\text{mA}$ , $I_B = 350\mu\text{A}$<br>$I_C = 350\text{mA}$ , $I_B = 500\mu\text{A}$                      |      | 0.9<br>1.1<br>1.3 | 1.1<br>1.3<br>1.6 | V             | 2<br>2<br>2 |

|                      |                                      |                                                                                                                                                                      |      | 1.3               |                   | V             |             |

| $I_{(on)}$           | Input Current                        | for <b>ULN2002A</b> , $V_i = 17\text{V}$                                                                                                                             |      | 0.82              | 1.25              | $\text{mA}$   | 3           |

|                      |                                      | for <b>ULN2003A</b> , $V_i = 3.85\text{V}$                                                                                                                           |      | 0.93              | 1.35              | $\text{mA}$   | 3           |

|                      |                                      | for <b>ULN2004A</b> , $V_i = 5\text{V}$                                                                                                                              |      | 0.35              | 0.5               | $\text{mA}$   | 3           |

|                      |                                      | $V_i = 12\text{V}$                                                                                                                                                   |      | 1                 | 1.45              | $\text{mA}$   | 3           |

| $I_{(off)}$          | Input Current                        | $T_{amb} = 70^\circ\text{C}$ , $I_C = 500\mu\text{A}$                                                                                                                | 50   | 65                |                   | $\mu\text{A}$ | 4           |

| $V_{(on)}$           | Input Voltage                        | $V_{CE} = 2\text{V}$<br>for <b>ULN2002A</b><br>$I_C = 300\text{mA}$                                                                                                  |      |                   | 13                | V             | 5           |

|                      |                                      | for <b>ULN2003A</b><br>$I_C = 200\text{mA}$                                                                                                                          |      |                   | 2.4               |               |             |

|                      |                                      | $I_C = 250\text{mA}$                                                                                                                                                 |      |                   | 2.7               |               |             |

|                      |                                      | $I_C = 300\text{mA}$                                                                                                                                                 |      |                   | 3                 |               |             |

|                      |                                      | for <b>ULN2004A</b><br>$I_C = 125\text{mA}$                                                                                                                          |      |                   | 5                 |               |             |

|                      |                                      | $I_C = 200\text{mA}$                                                                                                                                                 |      |                   | 6                 |               |             |

|                      |                                      | $I_C = 275\text{mA}$                                                                                                                                                 |      |                   | 7                 |               |             |

|                      |                                      | $I_C = 350\text{mA}$                                                                                                                                                 |      |                   | 8                 |               |             |

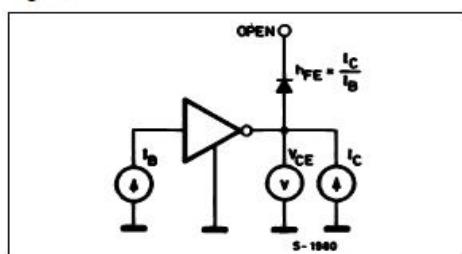

| $h_{FE}$             | DC Forward Current Gain              | for <b>ULN2001A</b><br>$V_{CE} = 2\text{V}$ , $I_C = 350\text{mA}$                                                                                                   | 1000 |                   |                   |               | 2           |

| $C_i$                | Input Capacitance                    |                                                                                                                                                                      |      | 15                | 25                | $\text{pF}$   |             |

| $t_{PLH}$            | Turn-on Delay Time                   | 0.5 $V_i$ to 0.5 $V_o$                                                                                                                                               |      | 0.25              | 1                 | $\mu\text{s}$ |             |

| $t_{PHL}$            | Turn-off Delay Time                  | 0.5 $V_i$ to 0.5 $V_o$                                                                                                                                               |      | 0.25              | 1                 | $\mu\text{s}$ |             |

| $I_R$                | Clamp Diode Leakage Current          | $V_R = 50\text{V}$<br>$T_{amb} = 70^\circ\text{C}$ , $V_R = 50\text{V}$                                                                                              |      |                   | 50<br>100         | $\mu\text{A}$ | 6<br>6      |

| $V_F$                | Clamp Diode Forward Voltage          | $I_F = 350\text{mA}$                                                                                                                                                 |      | 1.7               | 2                 | V             | 7           |

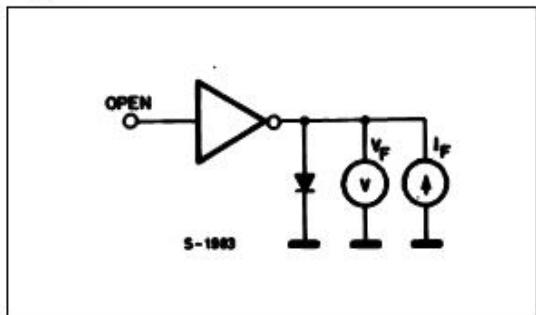

**TEST CIRCUITS**

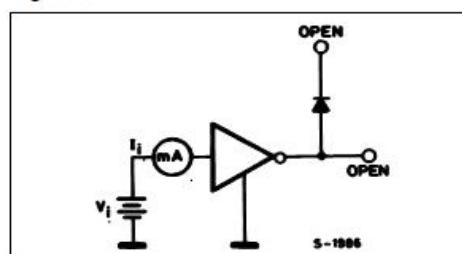

Figure 1a.

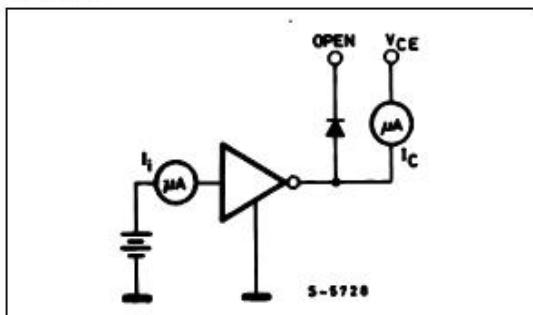

Figure 1b.

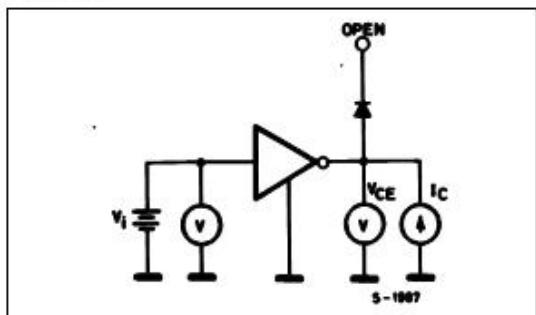

Figure 2.

Figure 3.

Figure 4.

Figure 5.

Figure 6.

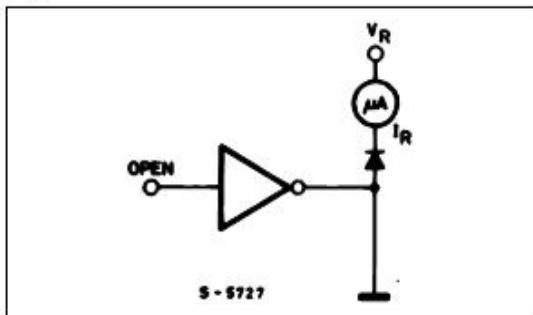

Figure 7.

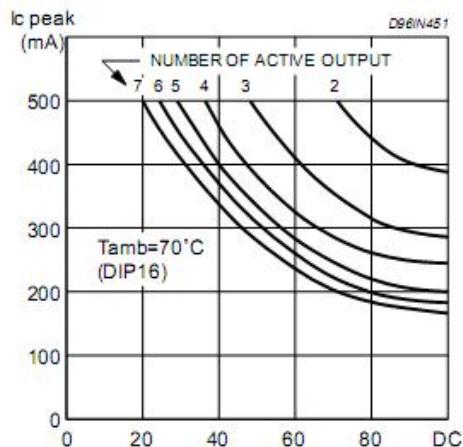

Figure 10: Peak Collector Current versus Duty Cycle

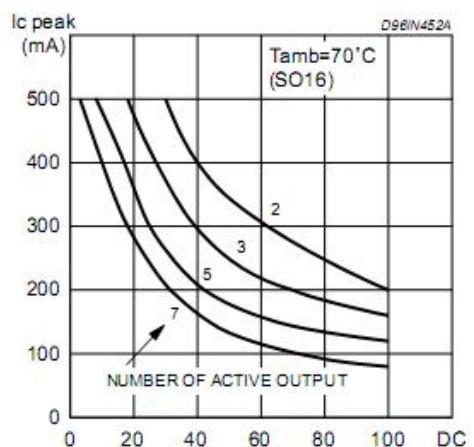

Figure 11: Peak Collector Current versus Duty Cycle

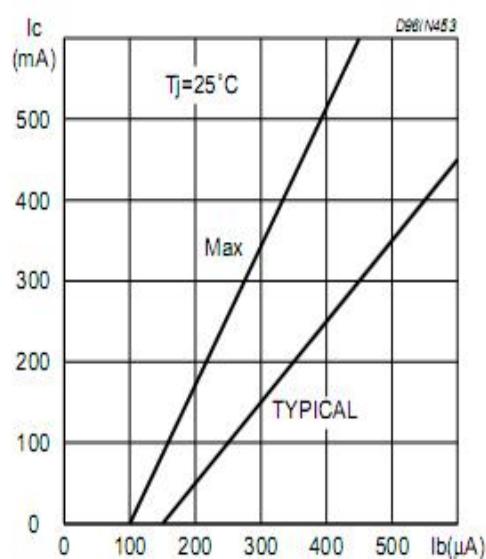

Figure 8: Collector Current versus Input Current

Figure 9: Collector Current versus Saturation Voltage

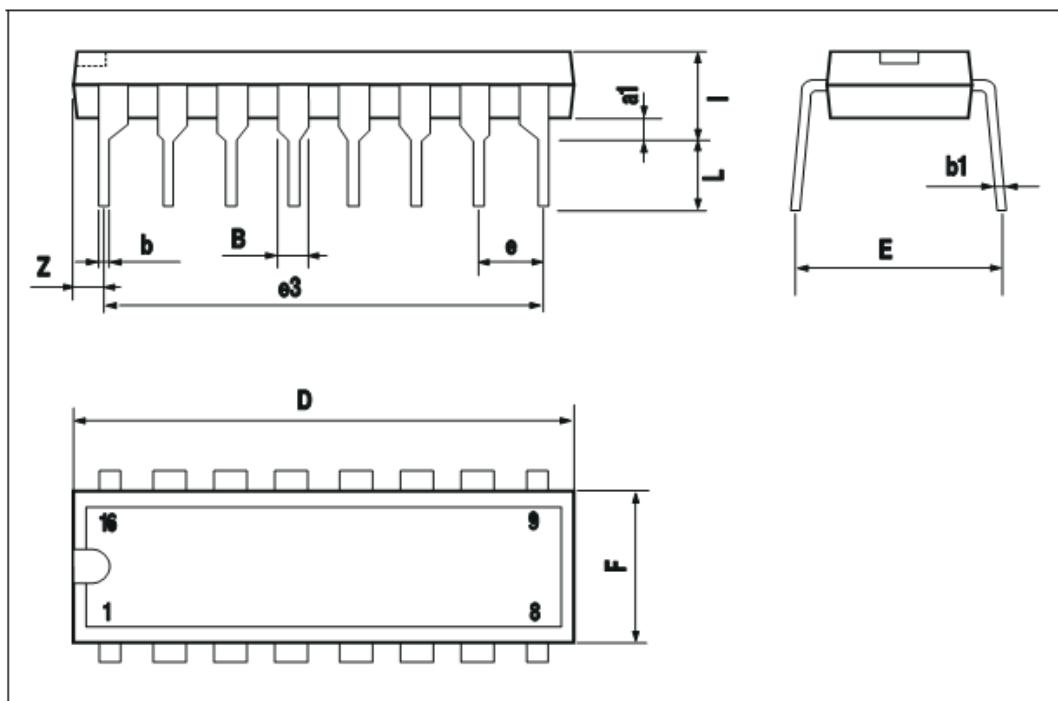

| DIM. | mm   |       |      | inch  |       |       |

|------|------|-------|------|-------|-------|-------|

|      | MIN. | TYP.  | MAX. | MIN.  | TYP.  | MAX.  |

| a1   | 0.51 |       |      | 0.020 |       |       |

| B    | 0.77 |       | 1.65 | 0.030 |       | 0.065 |

| b    |      | 0.5   |      |       | 0.020 |       |

| b1   |      | 0.25  |      |       | 0.010 |       |

| D    |      |       | 20   |       |       | 0.787 |

| E    |      | 8.5   |      |       | 0.335 |       |

| e    |      | 2.54  |      |       | 0.100 |       |

| e3   |      | 17.78 |      |       | 0.700 |       |

| F    |      |       | 7.1  |       |       | 0.280 |

| I    |      |       | 5.1  |       |       | 0.201 |

| L    |      | 3.3   |      |       | 0.130 |       |

| Z    |      |       | 1.27 |       |       | 0.050 |

| DIM.  | mm         |      |      | inch  |       |       |

|-------|------------|------|------|-------|-------|-------|

|       | MIN.       | TYP. | MAX. | MIN.  | TYP.  | MAX.  |

| A     |            |      | 1.75 |       |       | 0.069 |

| a1    | 0.1        |      | 0.25 | 0.004 |       | 0.009 |

| a2    |            |      | 1.6  |       |       | 0.063 |

| b     | 0.35       |      | 0.46 | 0.014 |       | 0.018 |

| b1    | 0.19       |      | 0.25 | 0.007 |       | 0.010 |

| C     |            | 0.5  |      |       | 0.020 |       |

| c1    | 45° (typ.) |      |      |       |       |       |

| D (1) | 9.8        |      | 10   | 0.386 |       | 0.394 |

| E     | 5.8        |      | 6.2  | 0.228 |       | 0.244 |

| e     |            | 1.27 |      |       | 0.050 |       |

| e3    |            | 8.89 |      |       | 0.350 |       |

| F (1) | 3.8        |      | 4    | 0.150 |       | 0.157 |

| G     | 4.6        |      | 5.3  | 0.181 |       | 0.209 |

| L     | 0.4        |      | 1.27 | 0.016 |       | 0.050 |

| M     |            |      | 0.62 |       |       | 0.024 |

| S     | 8°(max.)   |      |      |       |       |       |

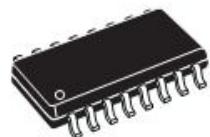

#### OUTLINE AND MECHANICAL DATA

SO16 Narrow

(1) D and F do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.15mm (.006inch).